Low Power High Performance ADC/Touch Key Flash 8051 MCU

#### **Product Description:**

PL51T020 is 8-bit high performance microcontroller with fully integrated touch key functions eliminating the need for external components, 11-bit up to 8 channels ADC and other modules. With the flexible configurable options integrated, PL51T020 offers a reliable and easy way of implementing touch keys, ADC, multi-function combinations for their product applications.

With integrating up to 16 flexible touch keys (which including 4 touch keys could be shift from P2.7~P2.4 to P0.0~P0.3), PL51T020 offers the customers a reliable and easy way of implementing touch keys for the product applications.

Special algorithms are employed to reduce the possibility of false detections, increasing the touch switch application reliability under adverse environmental conditions. With auto-calibration, low operating current and low power one-key operating state, PL51T020 provides a simple and effective means of implementing touch switches in a wide range of applications.

For high reliability and low cost issues, PL51T020 builds in reliable watchdog timer (WDT) and low power detect (LPD) and low voltage reset (LVR) function. The excellent noise immunity and ESD protection ensure reliable operations in the adverse electrical environments.

PL51T020 internal integrates high precision RC oscillator to operate and switch dynamically between a range of operating modes using different clock sources to optimize microcontroller operation and minimize power consumption. The excellent noise immunity and ESD protection ensure reliable operations in the adverse electrical environments.

PL51T020 also supports three low power modes, idle mode, stop mode and sleep mode, to reduce power consumption. It supports to be wakeup speedy by touch Key action when work in the low power mode.

PL51T020 is communicating with the outside world with UART, I2C and SPI interfaces.

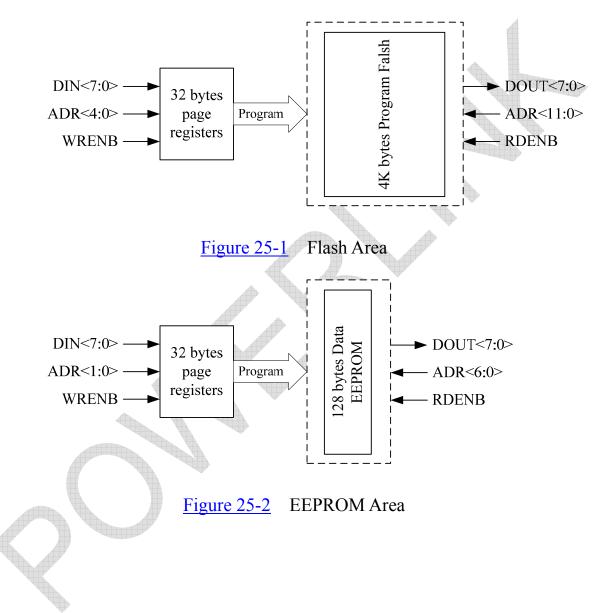

Besides the 4K bytes Flash program memory, other memory includes 256 bytes RAM and 128 bytes data EEPROM.

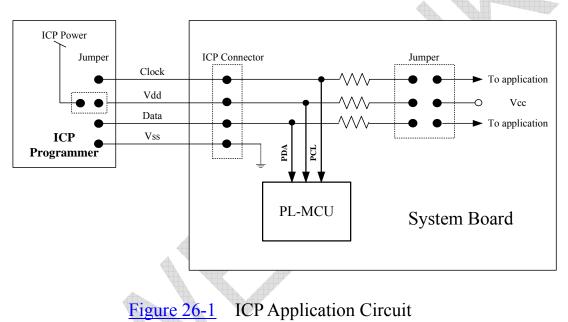

In-Circuit-Programming (ICP) supports the users to upgrade the program code and data in circuit without removing the microcontroller from the actual application board.

For easy usage, POWERLINK provides the debugger and writer.

#### Key Features:

- 1T Enhanced 8-Bit ET8051

- 4KB Flash and 128B EEPROM

- Fully integrated up to 16+4(shift) touch keys

- Operation Frequency@Voltage: ~4MHz@2.0~5.5V; ~8MHz@2.4~5.5V; ~12MHz@2.7~5.5V

- Operation Temperature: -40 °C ~+125 °C

- Supports Crystal Oscillator, internal 32KHz and high precision RC oscillator(4/8/12MHz, ±2%), external clock input

- Programmable System Clock

- Up to 22 bidirectional GPIO

- Four Priority Levels with 14 interrupt sources

- 8 Keyboard Interrupts

- 2 External Interrupts

- Support POR/LVR/LPD

- Three 16-bit Timers/Counters

- Four 12-bit PWM: PWM0/1/2/3

- Watchdog Timer with Prescaler

- Support UART/SPI/I2C interface

- Integrated Analog Comparator

- Integrated 11-bit 8 channels ADC

- Multi-mode Operation: Normal, Green, Stop, Sleep mode

- Support In-Circuit Programming

- Package: 24/20/16/8 PINs

- Memory Permission Control

- Flash Cycling: 100K @25℃

- EEPROM Cycling: 500K @25°C

- Data retention: 40 years @25°C

#### **Applications:**

- Wireless Mice, Keyboards and Game Controllers

- RF Remote Controller

- Small Home Appliances

# **Product Types**

| Product<br>Name | Package          | Program<br>Flash | Data<br>EEPROM <sup>*5</sup> | RAM  | Timer | PWM | Freq@Voltage  | I/O | Interface<br>UART/SPI/I2C | АСМР | T.S. | Touch Key <sup>*1</sup><br>/Wakeup(Max) | ADC <sup>*1</sup> |

|-----------------|------------------|------------------|------------------------------|------|-------|-----|---------------|-----|---------------------------|------|------|-----------------------------------------|-------------------|

|                 | Touch Key Series |                  |                              |      |       |     |               |     |                           |      |      |                                         |                   |

| PL51T020B24     | SSOP24           | 4KB              | 128B                         | 256B | 3     | 4+1 |               | 22  | 1/1/1                     | 1    | 1    | 16+4*3/16                               | 11b/8ch           |

| PL51T020N24     | QFN24            |                  |                              |      |       |     |               |     |                           |      |      |                                         |                   |

| PL51T020T20     | TSSOP20          | 4KB              | 128B                         | 256B | 3     | 4+1 | ~4M@2.0~5.5V  | 18  | 1/1/1                     | 1    | 1    | 12+4*2/16                               | 11b/4ch           |

| PL51T020N20     | QFN20            |                  |                              |      |       |     | ~ 8M@2.4~5.5V |     |                           |      |      |                                         |                   |

| PL51T020S16     | SOP16            | 4KB              | 128B                         | 256B | 3     | 4+1 | ~12M@2.7~5.5V | 14  | 1/1/1                     | -    | 1    | 8+4*2/12                                | 11b/4ch           |

| PL51T020N16     | QFN16            |                  |                              |      |       |     |               |     |                           |      |      |                                         |                   |

| PL51T020S8      | SOP8             | 4KB              | 128B                         | 256B | 3     | 4+1 |               | 6   | -                         | 1*4  | 1    | 3+2*2/5                                 | 11b/2ch           |

Note: \*1: Touch Key can't work with ADC at the same time, but can be set to work separately at different time slice.

- \*2: Shift Touch Keys <15:12> can be assigned as the touch keys <15:12> with wake-up function.

- \*3: Shift touch keys <15:12> or Original ones can be set to work separately at different time slice. Only Shift touch keys <15:12> or Original ones can be assigned as wake-up keys, separately.

- \*4: ACMP source, only between CMP1 and INTVREF (1.2V).

- \*5: In order to ensure that the Data EEPROM can be programmed stably, the LVR needs to be enabled and set to work greater than or equal to  $2.4V(\geq)$ .

# **Contents**

| PRODUCT DESCRIPTION:                         | 1  |

|----------------------------------------------|----|

| PRODUCT TYPES                                | 2  |

| CONTENTS                                     | 3  |

| 1 OVERVIEW                                   | 9  |

| 2 FEATURES                                   | 10 |

| 3 QUICK REFERENCE DATA                       |    |

| 4 PIN CONFIGURATIONS                         |    |

| 4.1 PIN DIAGRAMS                             |    |

| 4.2 PIN DESCRIPTION                          |    |

| 4.3 TERMINOLOGY AND SYMBOL CONVENTIONS       | 17 |

| 5 BLOCK DIAGRAM                              |    |

| 6 MEMORY ORGANIZATION                        | 19 |

| 6.1 PROGRAM MEMORY                           | 19 |

| 6.2 EXTERNAL DATA MEMORY                     | 20 |

| 6.3 DATA POINTER REGISTERS                   |    |

| 6.4 Internal Data Memory                     |    |

| 7 SPECIAL FUNCTION REGISTERS                 |    |

| 7.1 Special Function Registers Locations     | 21 |

| 7.2 Special Function Registers Reset Values  |    |

| 7.3 Special Function Registers Definition    |    |

| 7.3.1 Accumulator – ACC                      |    |

| 7.3.2 B Register – B                         |    |

| 7.3.3 Program Status Word Register - PSW     |    |

| 7.3.4 Stack Pointer - SP                     |    |

| 7.3.5 Data Pointer – DPH, DPL                |    |

| 7.3.6 Clock Control Register – CKCON         |    |

| 7.3.7 Timed Access Register – TA             |    |

| 7.3.8 SRST                                   | 30 |

| 8 ENHANCED CPU                               | 31 |

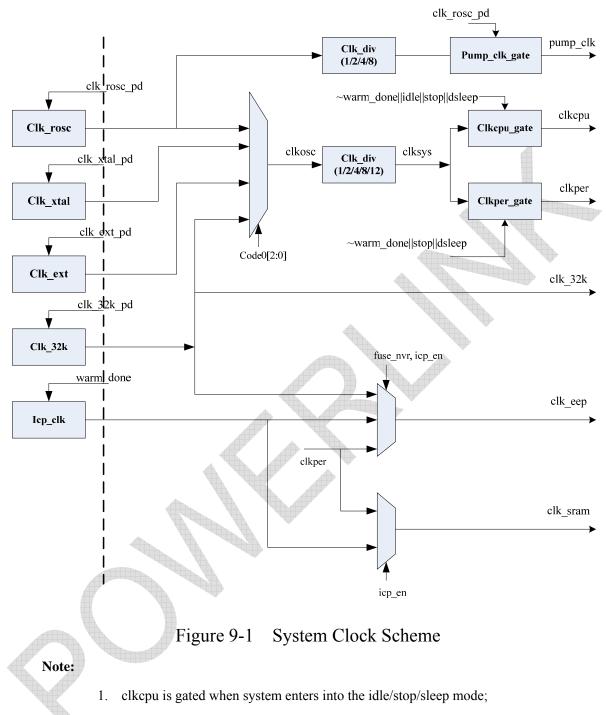

| 9 SYSTEM CLOCK                               | 32 |

| 9.1 Overview                                 | 32 |

| 9.2 Clock Definition                         |    |

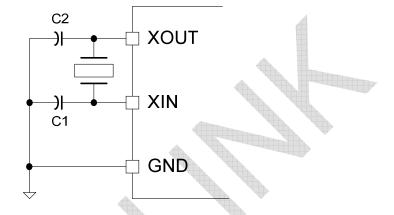

| 9.3 Crystal Oscillator and Ceramic Resonator | 33 |

| 9.4 INTERNAL 4/8/12MHz RC OSCILLATOR         | 34 |

| 9.5 External Clock                           |    |

| 9.6 INTERNAL 32KHz RC OSCILLATOR             | 34 |

| 9.7 System Clock Output                      | 34 |

| 9.8 Register Definition                            |    |

|----------------------------------------------------|----|

| 9.8.1 System Clock Prescaler Register - SCKCON     | 35 |

| 10 RESET                                           |    |

| 10.1 Overview                                      | 36 |

| 10.2 Power-on Reset                                |    |

| 10.3 Low Voltage Reset                             |    |

| 10.4 Low Power Detect                              |    |

| 10.5 External Reset                                |    |

| 10.6 Hardware Watchdog Reset                       |    |

| 10.7 Register Definition                           |    |

| 10.7.1 Reset Control Register - RSTCON             |    |

| 11 POWER SAVING MODES                              |    |

| 11.1 Overview                                      |    |

| 11.2 IDLE MODE                                     |    |

| 11.3 STOP Mode                                     |    |

| 11.4 SLEEP MODE                                    |    |

| 11.5 Register Definition                           |    |

| 11.5.1 Power Control Register - PCON               |    |

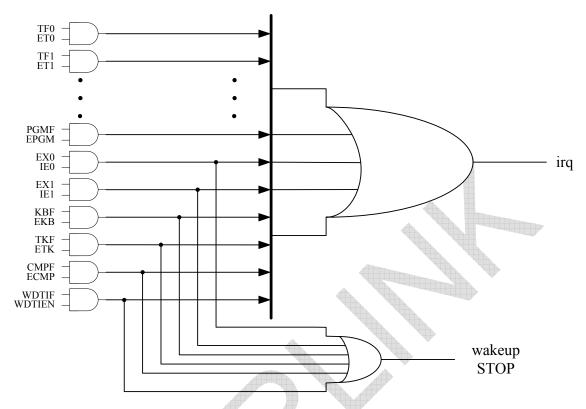

| 12 INTERRUPTS                                      |    |

|                                                    |    |

| 12.1 Overview                                      |    |

| 12.2 Interrupt Sources                             |    |

| 12.3 Priority Level Structure                      |    |

| 12.4 Response Time                                 |    |

| 12.5 Interrupt Inputs                              |    |

| 12.6 Register Definition                           |    |

| 12.6.1 Interrupt Enable 0 Register – IE0           |    |

| 12.6.2 Interrupt Enable 1 Register – IE1           |    |

| 12.6.3 Interrupt Request Control Register - IRCON  |    |

| 12.6.4 Interrupt Priority 0 Register – IP0         |    |

| 12.6.5 Interrupt High Priority 0 Register – IP0H   |    |

| 12.6.6 Interrupt Priority 1 Register – IP1         |    |

| 12.6.7 Interrupt High Priority 1 Register – IP1H   |    |

| 13 EXTERNAL INTERRUPTS                             |    |

| 14 KEYBOARD INTERFACE                              | 53 |

| 14.1 Register Definition                           |    |

| 14.1.1 Keyboard Interrupt Control Register – KBCON | 53 |

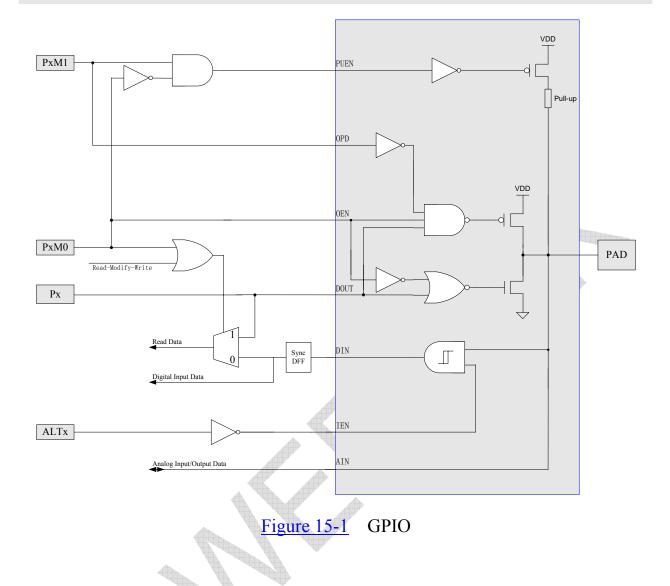

| 15 I/O PORTS                                       | 54 |

| 15.1 Overview                                      | 54 |

| 15.2 Port Configuration                            |    |

| 15.3 Port Analog Functions                         |    |

|                                                    |    |

| 15.4 Port  | Read-Modify-Write                                        | 55 |

|------------|----------------------------------------------------------|----|

| 15.5 Port  | ALTERNATE FUNCTIONS                                      | 56 |

| 15.6 REGIS | STER DEFINITION                                          | 61 |

| 15.6.1     | Port 0 Data Register – P0                                | 61 |

| 15.6.2     | Port 0 Control Registers – P0M0/P0M1                     | 61 |

| 15.6.3     | Port 1 Data Register – P1                                | 61 |

| 15.6.4     | Port 1 Control Registers – P1M0/P1M1                     | 61 |

| 15.6.5     | Port 2 Data Register – P2                                | 62 |

| 15.6.6     | Port 2 Control Registers – P2M0/P2M1                     |    |

| 15.6.7     | Port Analog Switch Registers – ASW0/ASW1                 |    |

| 15.6.8     | Port shift Register – PSFT0                              | 63 |

| 15.6.9     | Port shift Register – PSFT1                              |    |

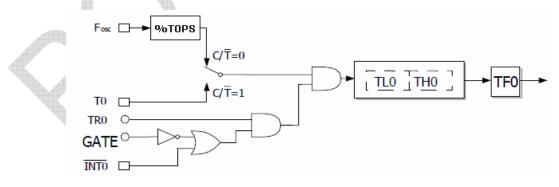

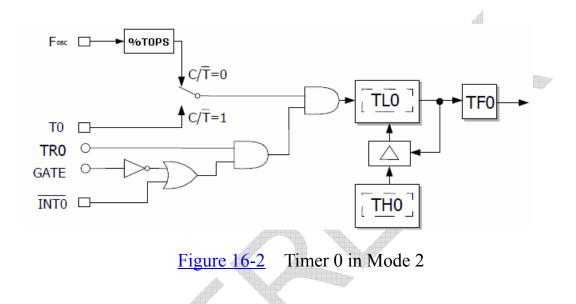

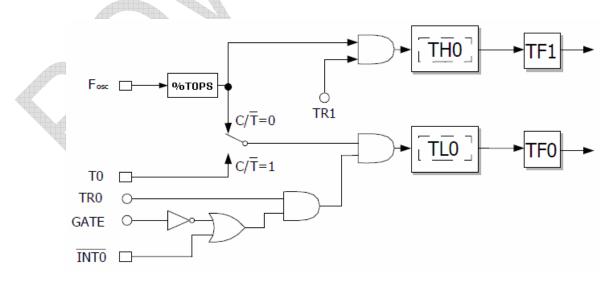

| 16 TIMER ( | ) AND TIMER 1                                            |    |

| 16.1 Over  | RVIEW                                                    | 64 |

| 16.2 MOD   | e 0 and Mode 1                                           | 64 |

| 16.3 MOD   | E 2                                                      | 65 |

| 16.4 MOD   | E 3                                                      | 65 |

| 16.5 REGIS | STER DEFINITION                                          |    |

| 16.5.1     | Timer/Counter Control Register - TCON                    |    |

| 16.5.2     | Timer Mode Register - TMOD                               |    |

| 16.5.3     | Timer Clock Prescaler Register - TCKCON                  | 68 |

| 16.5.4     | Timer 0 Registers – TH0/TL0                              | 69 |

| 16.5.5     | Timer 1 Registers – TH1/TL1                              | 69 |

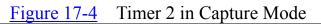

| 17 TIMER 2 | 2                                                        |    |

|            | RVIEW                                                    |    |

|            | R FUNCTION                                               |    |

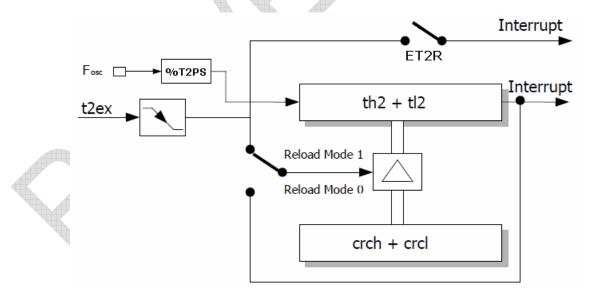

| 17.2.1     | Timer Mode                                               |    |

| 17.2.2     | Timer 2 Reload Mode                                      |    |

|            | PARE FUNCTION                                            |    |

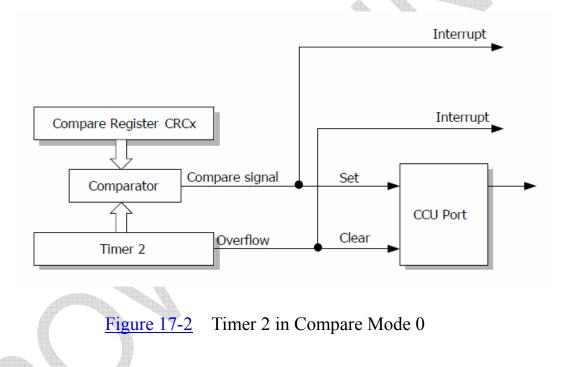

| 17.3.1     | Compare Mode 0                                           |    |

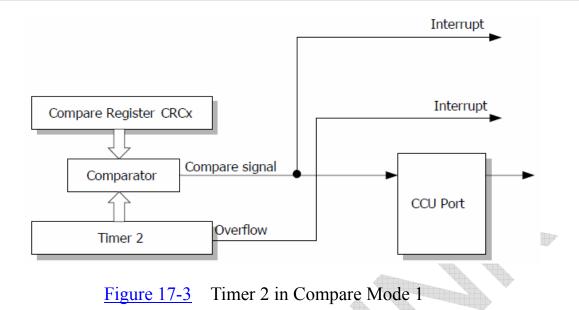

| 17.3.2     | Compare Mode 1                                           |    |

|            | URE FUNCTION                                             |    |

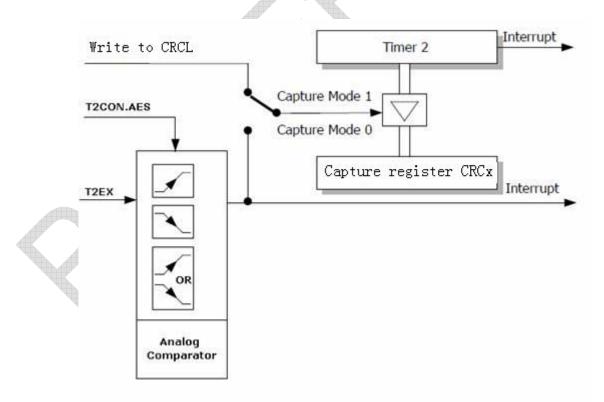

| 17.4.1     | Capture Mode 0                                           |    |

| 17.4.2     | Capture Mode 1                                           |    |

| 17.5 PWN   | 1 FUNCTION                                               |    |

|            | STER DEFINITION                                          |    |

| 17.6.1     | Timer 2 Control Register – T2CON                         | 74 |

| 17.6.2     | Timer 2 Mode Register – T2MOD                            |    |

| 17.6.3     | Timer 2 Compare/Reload/Capture/PWM Registers – CRCH/CRCL |    |

| 17.6.4     | Timer 2 Registers – TH2/TL2                              |    |

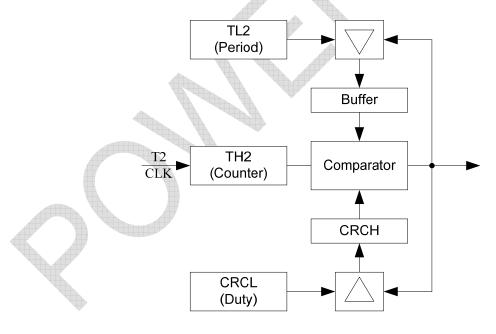

| 18 PWM0/1  | /2/3                                                     |    |

|            |                                                          |    |

| 18.1 OVER  | RVIEW                                                    | /0 |

| 18.2 REGIS           | TER DEFINITION                                 | 76        |

|----------------------|------------------------------------------------|-----------|

| 18.2.1               | PWM Control Register – PWMCON0                 |           |

| 18.2.2               | PWM0 Period Registers – PWM0PH/PWM0PL          | 77        |

| 18.2.3               | PWM0 Duty Registers – PWM0DH/PWM0DL            |           |

| 18.2.4               | PWM1 Period Registers – PWM1PH/PWM1PL          |           |

| 18.2.5               | PWM1 Duty Registers – PWM1DH/PWM1DL            |           |

| 18.2.6               | PWM2 Period Registers – PWM2PH/PWM2PL          |           |

| 18.2.7               | PWM2 Duty Registers – PWM2DH/PWM2DL            |           |

| 18.2.8               | PWM3 Period Registers – PWM3PH/PWM3PL          |           |

| 18.2.9               | PWM3 Duty Registers – PWM3DH/PWM3DL            |           |

| 10 ЖАТСИГ            | OG TIMER                                       | <b>Q1</b> |

|                      |                                                |           |

| 19.1 Regis           | TER DEFINITION                                 |           |

| 19.1.1               | WDT Control Register – WDTCON                  |           |

| 20 UART              |                                                |           |

|                      | 0                                              |           |

|                      |                                                |           |

|                      | 1                                              |           |

|                      |                                                |           |

|                      | 3                                              |           |

|                      | Rате                                           |           |

|                      | ERIAL PORT MULTIPROCESSOR COMMUNICATION        |           |

|                      | TER DEFINITION                                 |           |

| 20.7.1               | Serial Port Control Register – SCON            |           |

| 20.7.2               | Serial Port Data Buffer – SBUF                 |           |

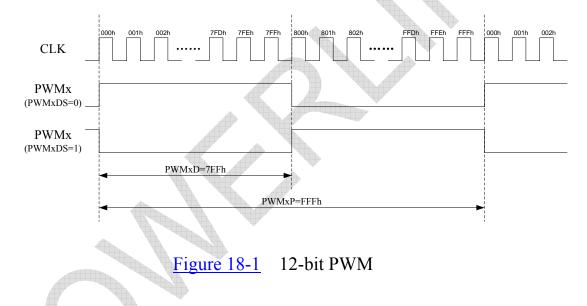

| 21 SPI               |                                                |           |

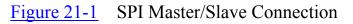

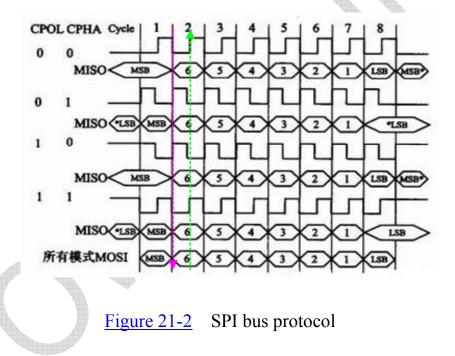

| 21 1 SPLIN           | TERFACE                                        | 87        |

|                      | DMMUNICATION                                   |           |

|                      | TER DEFINITION                                 |           |

| 21.3 142015          | SPI Serial Peripheral Status Register – SPSTA  |           |

| 21.3.1               | SPI Serial Peripheral Control Register – SPCON |           |

| 21.3.2               | SPI Serial Peripheral Data Register – SPDAT    |           |

|                      |                                                |           |

| 22 I2C               |                                                | 91        |

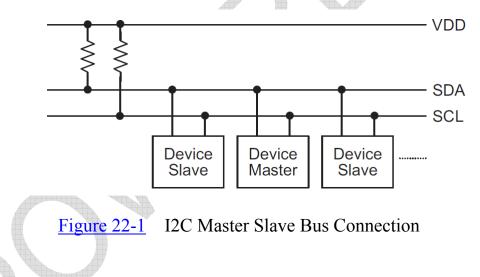

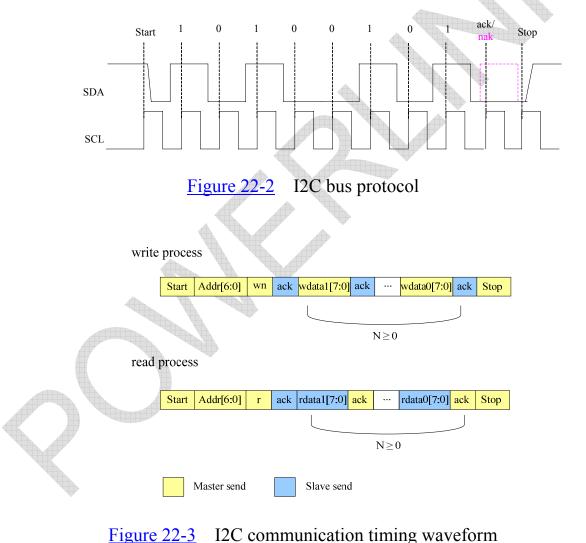

| 22.1 I2C IN          | TERFACE                                        | 91        |

| 22.2 I2C C           | OMMUNICATION                                   | 91        |

| 22.3 REGIS           | TER DEFINITION                                 | 93        |

| 22.3.1               | I2C Status Register – I2CSTA                   |           |

| 22.3.2               | I2C Control Register – I2CCON                  |           |

| 22.3.3               | I2C Address Register – I2CADR                  |           |

| 22.3.4               | I2C Data Register – I2CDAT                     |           |

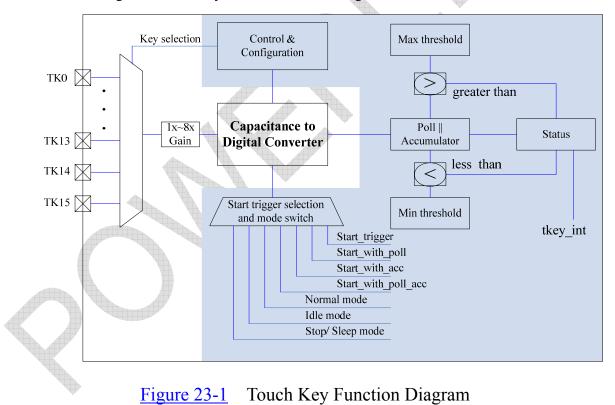

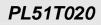

| 23 A/D & TC          | UCHKEY                                         | 96        |

| 23.1 Over            | /IEW                                           |           |

| 23.1.0 VER<br>23.1.1 | Touch Key Operation                            |           |

| 20.1.1               |                                                |           |

| 23.1.2       | Touch Key & ADC Interrupt                            |     |

|--------------|------------------------------------------------------|-----|

| 23.1.3       | Touch Key Work Mode                                  |     |

| 23.2 REGIS   | TER DEFINITION                                       |     |

| 23.2.1       | Touch Key Registers Address Map                      |     |

| 23.2.2       | Touch key Data Register – TKDATL                     |     |

| 23.2.3       | Touch key Data Register – TKDATH                     |     |

| 23.2.4       | Touch key7-0 select Register – TKCHS0                |     |

| 23.2.5       | Touch key15-8 select Register – TKCHS1               |     |

| 23.2.6       | Touch key control Register – TKCON0                  |     |

| 23.2.7       | Touch key control Register – TKCON1                  |     |

| 23.2.8       | Touch key control Register – TKCON2                  |     |

| 23.2.9       | Touch key status Register – TKADCF                   |     |

| 23.2.10      | Touch key status Register – TKCSCF                   |     |

| 23.2.11      | Touch key status Register – TKCSOF                   |     |

| 23.2.12      | Touch key Wakeup threshold Register – TKWKL0         |     |

| 23.2.13      | Touch key Wakeup threshold Register – TKWKH0         |     |

| 23.2.14      | Touch key Wakeup threshold Register – TKWKL1         |     |

| 23.2.15      | Touch key Wakeup threshold Register – TKWKH1         |     |

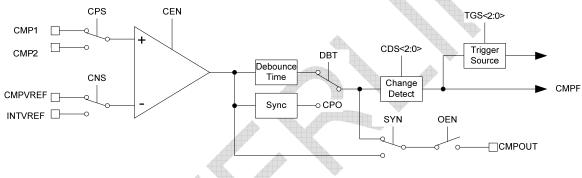

| 24 ANALOG    | COMPARATOR                                           |     |

|              | /IEW                                                 |     |

|              |                                                      |     |

|              | TER DEFINITION                                       |     |

| 24.2.1       | Comparator Control Register 0 – CMPCON0              |     |

| 24.2.2       | Comparator Control Register 1 – CMPCON1              |     |

| 25 FLASH &   | EEPROM                                               | 111 |

| 25.1 Мемс    | DRY ENCRYPTION                                       | 111 |

| 25.2 REGIS   | TER DEFINITION                                       |     |

| 25.2.1       | EEPROM Control Register – EECON                      | 112 |

| 26 ICP (IN-C | CIRCUIT PROGRAMMING)                                 | 113 |

| 26.1 Overv   | /IEW                                                 |     |

|              | OPTIONS                                              |     |

|              | ICAL CHARACTERISTICS                                 |     |

|              |                                                      |     |

|              | UTE MAXIMUM RATINGS                                  |     |

|              | ECTRICAL CHARACTERISTICS                             |     |

|              | ECTRICAL CHARACTERISTICS                             |     |

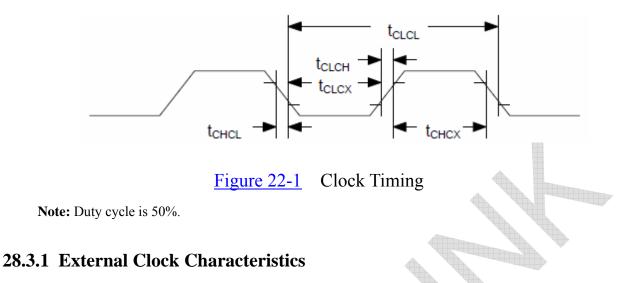

| 28.3.1       | External Clock Characteristics                       |     |

| 28.3.2       | Internal RC OSC Characteristics                      |     |

| 28.3.3       | Crystal Oscillator/Ceramic Resonator Characteristics |     |

|              | ARATOR ELECTRICAL CHARACTERISTICS                    |     |

|              | APPLICATION                                          |     |

| 29.1 Touch   | ікеу Demo                                            | 117 |

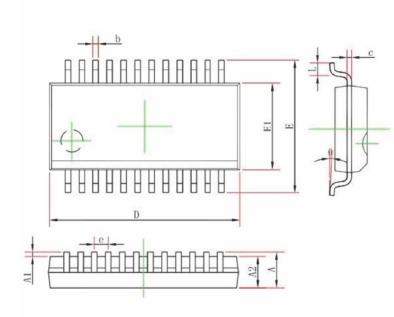

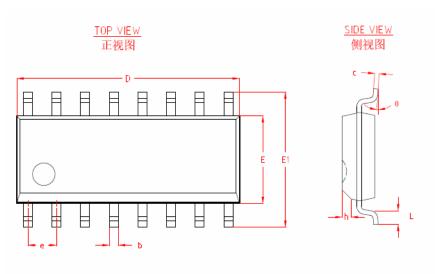

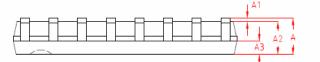

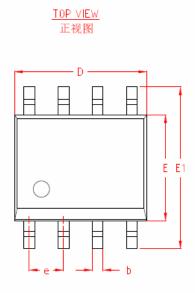

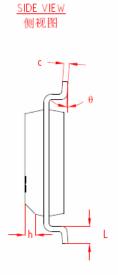

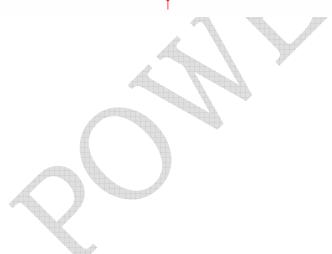

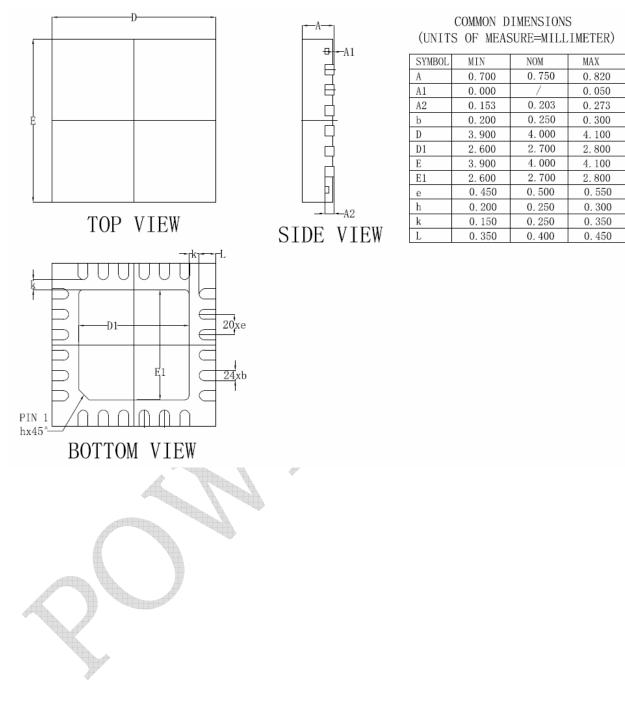

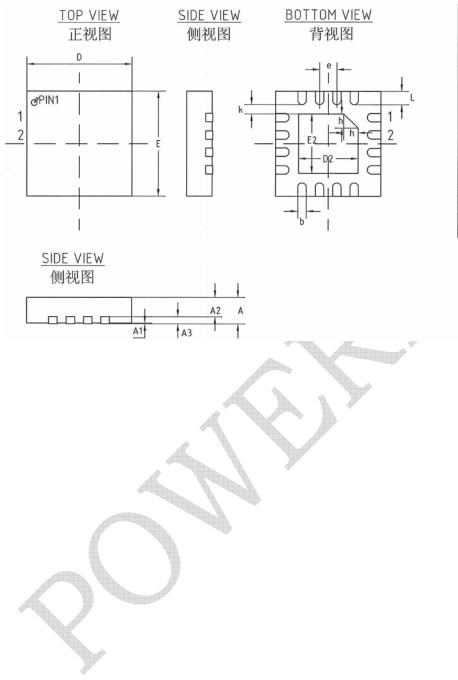

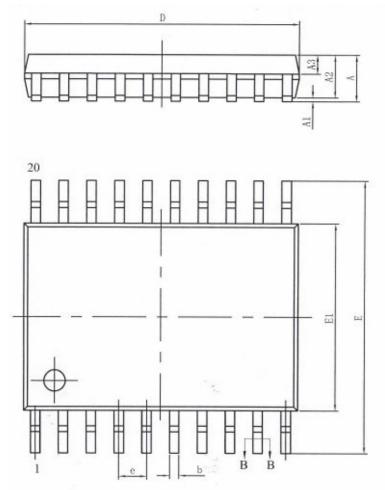

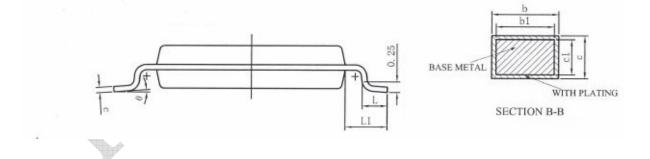

| 30 PACKAGE DIMENSIONS        |  |

|------------------------------|--|

| 30.1 SSOP24 Package          |  |

| 30.2 SOP16 PACKAGE           |  |

| 30.3 SOP8 PACKAGE            |  |

| 30.4 QFN24 Package           |  |

| 30.5 QFN20 PACKAGE           |  |

| 30.6 QFN16 Package           |  |

| 30.7 TSSOP20 PACKAGE         |  |

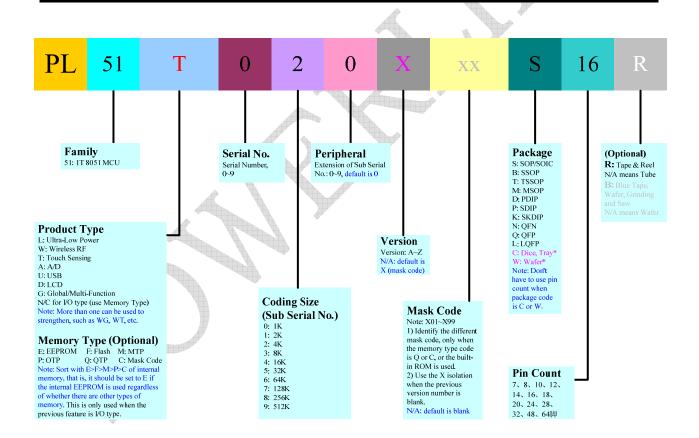

| 31 ORDERING INFORMATION      |  |

| 32 DOCUMENT REVISION HISTORY |  |

| 33 IMPORTANT NOTICE          |  |

# **1** Overview

PL51T020 series are а single-chip microcontroller based on a high performance 1T architecture 80C51 CPU which have a fully compatible instruction set with standard 80C51 series microcontroller, and execute instructions in 1~4 clock cycles (about 7~8 times the rate of a standard 8051 chip). The PL51T020 series have a 22 bi-direction GPIO, a 14-source (including 2 external interrupt sources), 4-priority-level interrupt structure, a fully integrated touch key function without the need for external components.

With integrating up to 16 flexible touch keys (which including 4 touch keys could be shift from P2.7~P2.4 to P0.0~P0.3), PL51T020 offers the customers a reliable and easy way of implementing touch keys for the product applications.

Special algorithms are employed to reduce the possibility of false touch action identifications, improving the touch key application reliability under adverse environmental conditions. With supporting auto calibration configuration, touch key could be working at a wide range of dynamic capacitance with low power consumption and high sensitivity identification.

For high reliability and low cost issues, PL51T020 builds in reliable watchdog timer (WDT), low power detect (LPD) and low voltage reset (LVR) functions. The excellent noise immunity and ESD protection ensure reliable operations in the adverse electrical environments.

PL51T020 integrates low and high frequency oscillators to operate and switch dynamically between a range of operating modes using different clock sources to optimize microcontroller operation and minimize power consumption.

In order to reduce power consumption, PL51T020 could be work in three low power modes, green mode, stop mode and sleep mode, it supports to be wakeup speedy by keyboard action when work in the low power mode.

PL51T020 is communicating with the outside world with UART, I2C and SPI interfaces.

Besides the 4K bytes flash program memory with Memory-Permission-Control, other memory includes 256 bytes RAM Data Memory as well as 128 bytes EEPROM memory is integrated.

In-Circuit-Programming (ICP) support the users to upgrade the program code and data in circuit without removing the microcontroller from the actual application board.

For easy usage, POWERLINK provides the debugger and writer.

PL51T020 is targeting at home appliance such as Wireless Mice, Keyboards and Game Controllers, RF Remote Controller, Induction cooker, Microwave oven, Washing machine, Clothes dryer, Dishwasher, Refrigerator, Air conditioner and etc.

### PL51T020

# 2 Features

#### 📕 Basic

- ♦ 1T 8-bit ET8051 core

- ✤ Fully integrated 16 touch key functions with no external components

- ♦ Operating Voltage @ Frequency:

- ✓ ~4MHz@2.0~5.5V

- ✓ ~8MHz@2.4~5.5V

- ✓ ~12MHz@2.7~5.5V

- ♦ Oscillator Type

- ✓ Crystal Oscillator: 400KHz to 12MHz

#### **4** Peripheral Features

- ✤ Four Priority Levels with 14 interrupt sources

- ✓ Two External Interrupt: INT0B and INT1B

- ✓ T0&T1 Overflow Interrupt

- ✓ T2 Overflow, Reload, Compare/Capture Interrupt

- ✓ UART Transmit and Receive Interrupt

- ✓ EEPROM Write Finished Interrupt

- ✓ Analog Comparator Interrupt

- Keyboard Interrupt

- ✓ Touch Key Interrupt

- ✓ SPI Interrupt

- ✓ I2C Interrupt

- ✓ ADC Finish Converting Interrupt

- ♦ POR/LVR/LPD support

- ♦ Four LVR threshold Level by Fuse:

- ✓ 2.1/2.4/3.7/4.3 V

- ✓ Internal RC Oscillator: 4/8/12MHz (±2%) and 32KHz

- ✓ External Clock: 400KHz to 12MHz

- ♦ Up to 22 bidirectional General Purpose I/O

- ✓ Input-Only with configurable pull high resistor

- ✓ Push-Pull Output Drive Capacity: 20mA (@5V, Total: <100mA)</li>

- Operation Temperature: -40℃ to +125℃

- ♦ Two LPD threshold Level by Fuse:

- ✓ 2.7/4.0 V

- ♦ Register Timed Access Protection

- ♦ Programmable System Clock

- ♦ Multi-mode Operation:

- ✓ Normal/Idle/Stop/Sleep

- ♦ 16-bit Timers/Counters:

- ✓ 80C51-like Timer 0 & 1

- ✓ 8052-like Timer 2 with Compare/Capture Unit (CCU)

- ♦ Four 12-bit PWM: PWM0/1/2/3

- Watchdog Timer with Additional Configurable Prescaler: WDT

- ♦ UART/SPI/I2C Interface

- ♦ Analog Digital Converter: ADC

- ✓ 11-bit resolution

- ✓ Up to 8 multiplexed channels

- ✓ support external input VREF

### ♦ 4K bytes Program Flash

EFT: >4KV

$\Leftrightarrow$  ESD: >2KV (HBM)

$\diamond$

∻

∻

📥 Memory

Datasheet (Preliminary Version)

Support In-Circuit Programming: ICP

Analog Comparator: ACMP

- ♦ 256 bytes internal scratch-pad RAM

- Memory Programming Permission Control

- ♦ Package Types

- ✓ SOP8/SOP16/TSSOP20/SSOP24

- ✓ QFN16/QFN20/QFN24

- ♦ Flash Cycling: 100K @25°C

- ♦ EEPROM Cycling: 500K @25°C

- ♦ Data retention: 40 years @25°C

# **3 Quick Reference Data**

|                                        | · · ·       |       |

|----------------------------------------|-------------|-------|

| Parameter                              | Value       | Units |

| Min Supply Voltage                     | 2.0         | V     |

| Operating Temperature Range            | -40 to +125 | °C    |

| Internal RC OSC Frequency              | 4/8/12      | MHz   |

| Internal RC OSC Precision @ 25°C       | ±2          | %     |

| Push-Pull Output Drive Capacity @ 5V   | 20          | mA    |

| Push-Pull Output Drive Capacity @ 3.3V | 10          | mA    |

| Total Push-Pull Output Drive Capacity  | <100        | mA    |

| Current Consumption @ Sleep Mode       | 1           | uA    |

# **4 Pin Configurations**

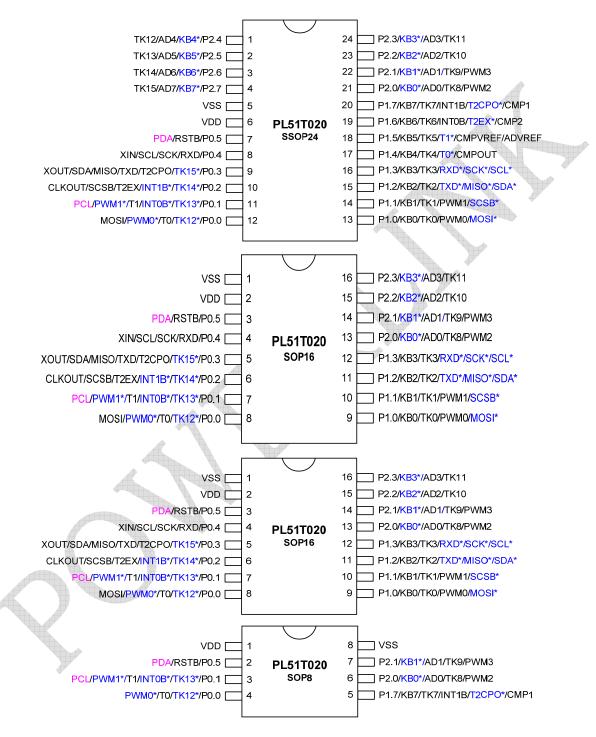

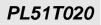

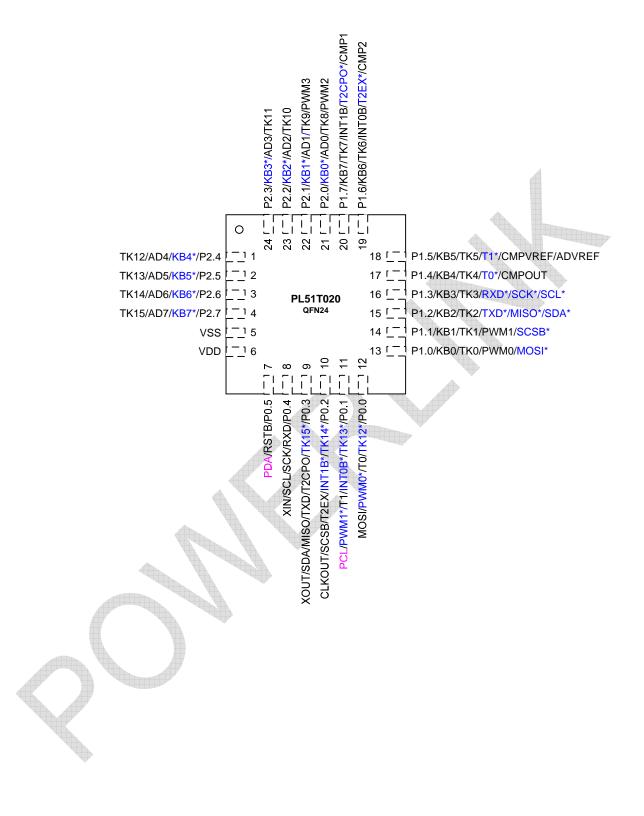

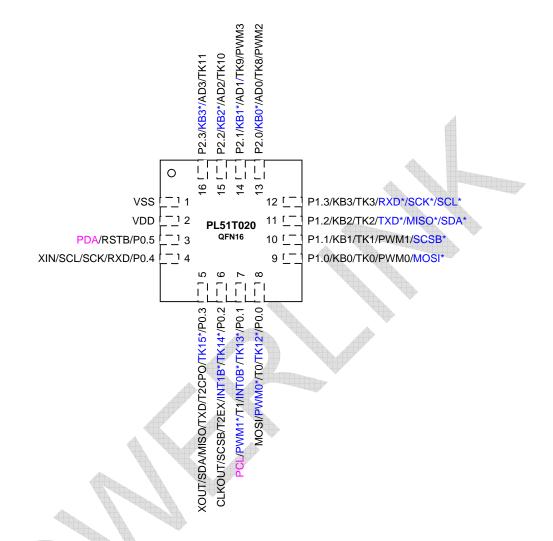

### **4.1 Pin Diagrams**

#### Note:

- The outside pin function has the highest priority, and the inner pin function has the lowest priority. It means that if the higher priority function is enabled, the lower priority function can't be used even when the lower priority function is also enabled.

- 2) The pin name colored blue with \* denoted the shift ports, the pin function available only when the relative shift control bit in SFR "PSFT0~1" is set.

# **4.2 Pin Description**

| Symbol    | Туре           | Descriptions                                             |

|-----------|----------------|----------------------------------------------------------|

| VDD       | Power          | Power Supply (2.0~5.5V)                                  |

| VSS       | Power          | Ground (0V)                                              |

| RSTB      | Digital Input  | Reset Pin, Active Low                                    |

| XIN       | Analog Input   | Crystal Oscillator Input                                 |

| XOUT      | Analog Output  | Crystal Oscillator Output                                |

| CLKOUT    | Digital Output | Internal Clock Output                                    |

| SCL       | Digital I/O    | Clock for I2C Interface                                  |

| SDA       | Digital I/O    | Data I/O for I2C Interface                               |

| SCSB      | Digital Input  | Enable Input for SPI Interface, active Low               |

| SCK       | Digital I/O    | Clock for SPI Interface                                  |

| MISO      | Digital I/O    | Master Data Input or Slave Data Output for SPI Interface |

| MOSI      | Digital I/O    | Master Data Output or Slave Data Input for SPI Interface |

| RXD       | Digital Input  | RXD of Serial Port                                       |

| TXD       | Digital Output | TXD of Serial Port                                       |

| Т0        | Digital Input  | Timer 0 Input                                            |

| T1        | Digital Input  | Timer 1 Input                                            |

| T2EX      | Digital Input  | Timer 2 External Capture Input                           |

| Т2СРО     | Digital Output | Timer 2 Compare/PWM Ouput                                |

| INT0B     | Digital Input  | External Interrupt 0                                     |

| INT1B     | Digital Input  | External Interrupt 1                                     |

| PWM0      | Digital Output | PWM 0 Output                                             |

| PWM1      | Digital Output | PWM 1 Output                                             |

| PWM2      | Digital Output | PWM 2 Output                                             |

| PWM3      | Digital Output | PWM 3 Output                                             |

| CMP1      | Analog Input   | Comparator Positive 1 Input                              |

| CMP2      | Analog Input   | Comparator Positive 2 Input                              |

| CMPVREF   | Analog Input   | Comparator Reference Voltage Input                       |

| CMPOUT    | Digital Output | Comparator Output                                        |

| TK0~15    | Analog Input   | Touch Key Inputs                                         |

| KB0~7     | Analog Input   | Keyboard Inputs                                          |

| P0.0~P0.5 | Digital I/O    | General purpose I/O Port 0                               |

| P1.0~P1.7 | Digital I/O    | General purpose I/O Port 1                               |

| P2.0~P2.7 | Digital I/O    | General purpose I/O Port 2                               |

| PCL       | Digital Input  | Clock Input for ICP (In Circuit Program) Mode            |

| PDA       | Digital I/O    | Data I/O for ICP (In Circuit Program) Mode               |

| ADVREF    | Analog Input   | ADC Reference Voltage Input                              |

| AD0~AD7   | Analog Input   | ADC Inputs                                               |

| Symbol | Description                    | Symbol | Description                             |

|--------|--------------------------------|--------|-----------------------------------------|

| CPU    | Control Processor Unit         | PFL    | Program Flash                           |

| ALU    | Arithmetic-Logic Unit          | DEE    | Data EEPROM                             |

| MSB    | Most Significant Bit           | NVR    | NVR EEPROM                              |

| LSB    | Least Significant Bit          | CEE    | Code Fuse EEPROM                        |

| SFR    | Special Function Register      | TEE    | Trim Fuse EEPROM                        |

| ISR    | Interrupt Service Routine unit | ІСР    | In-Circuit Programming                  |

| POR    | Power On Reset                 | ICD    | In-Circuit Debugging                    |

| LVR    | Low Voltage Reset              | ISP    | In-System Programming                   |

| LPD    | Low Power Detect               | TW     | Write operation is permitted only after |

|        |                                |        | open a window by 'TA' register          |

| PMU    | Power Management Unit          | SPI    | Serial Peripheral Interface             |

| PWM    | Pulse Width Modulation         | I2C    | Two-Wire Interface                      |

| WDT    | Watch Dog Timer                | UART   | Universal Asynchronous Receiver         |

|        |                                |        | Transmitter                             |

| CCU    | Compare/Capture Unit           | ADC    | Analog Digital Converter                |

| ТА     | Timed Access                   | DAC    | Digital Analog Converter                |

| ACMP   | Analog Comparator              | САР    | Capacitive Touch Sensor                 |

|        |                                |        |                                         |

# 4.3 Terminology and Symbol Conventions

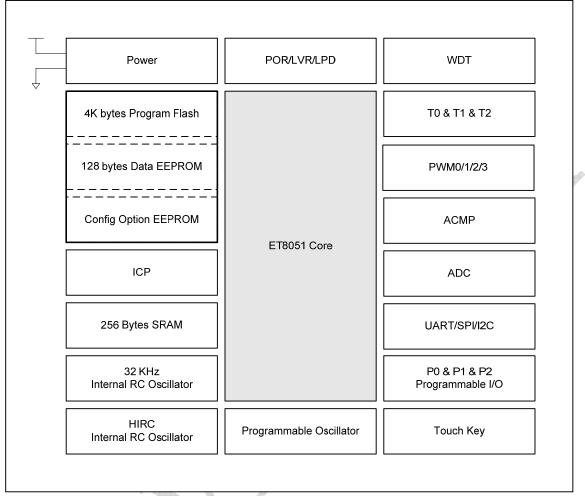

# **5 Block Diagram**

|        | Figure 5-1 | Block diagram |  |

|--------|------------|---------------|--|

|        |            |               |  |

|        |            |               |  |

| $\sim$ |            |               |  |

|        |            |               |  |

|        |            |               |  |

|        |            |               |  |

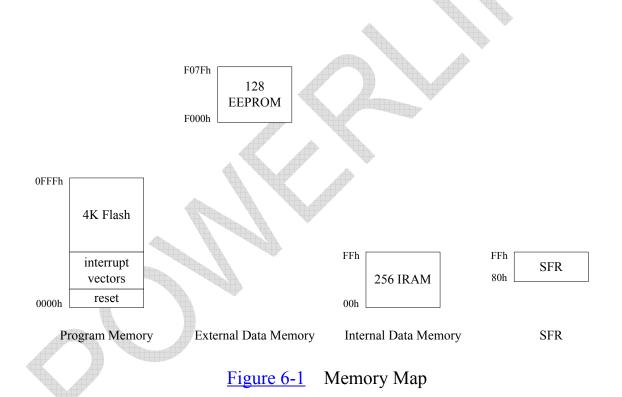

# **6 Memory Organization**

The ET8051 microcontroller core incorporates the Harvard architecture, with separate code and data spaces.

Memory organization in the ET8051 is similar to that of the industry standard 8051. There are three memory areas: Program Memory (Internal FLASH), External Data Memory (External EEPROM) and Internal Data Memory (Internal RAM).

The Program Memory includes 4K bytes program FLASH.

The External Data Memory includes 128 bytes data EEPROM.

The Internal Data Memory includes 256 bytes internal scratch-pad RAM.

### 6.1 Program Memory

Program memory is used for storing program code, after reset, the CPU starts program execution at location 0000h. The lower part of program memory includes interrupt and reset vectors. The interrupt vectors are spaced at 8-byte intervals, starting from 0003h.

### 6.2 External Data Memory

External data memory is used for data storage.

The 128 bytes data memory, it's address mapped into F000h~F07Fh.

### **6.3 Data Pointer Registers**

Data pointers accelerate data blocks moving. Data Pointer Register (DPTR) is a 16-bit register that is used to address external memory or peripherals.

The ET8051 includes one Data Pointer Register. The active Data Pointer Register can be accessed as SFRs: DPH, DPL.

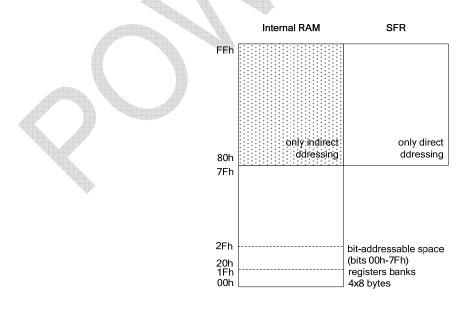

### 6.4 Internal Data Memory

The internal data memory interface services up to 256 bytes data memory. The memory space accommodates also 128 bytes of Special Function Registers.

Addresses lower than 80h access lower 128 bytes of internal data memory. Both direct and indirect addressing can be used in this case.

Indirect addressing of locations higher than 7Fh accesses upper 128 bytes of internal data memory, while direct addressing of locations higher than 7Fh accesses SFR space.

The lower 128 bytes contain work registers (00h ... 1Fh) and bit-addressable memory (20h ... 2Fh). The lowest 32 bytes form four banks, each consisting of eight registers (R0-R7). Two bits of the program memory status word (PSW) select which bank is in use. The next 16 bytes of memory form a block of bit-addressable memory, accessible via 00h-7Fh addresses.

# **7 Special Function Registers**

### 7.1 Special Function Registers Locations

The map of Special Function Registers is shown in the following Table. Some addresses are occupied, while the others are not implemented. Read & write access to unimplemented addresses will target the External SFR Interface.

| Hex/      | X000   | X001    | X010    | X011   | X100   | X101    | X110    | X111   | Bin/      |

|-----------|--------|---------|---------|--------|--------|---------|---------|--------|-----------|

| Bin       |        |         |         |        |        |         |         |        | Hex       |

| F8        | RSTCON | PWMCON1 | PWMCON0 | PWM0PL | PWM0PH | PWM0DL  | PWM0DH  | TA     | FF        |

| FO        | В      |         |         | PWM1PL | PWM1PH | PWM1DL  | PWM1DH  | SRST   | F7        |

| E8        | PWM2PL | PWM2PH  | PWM2DL  | PWM2DH | PWM3PL | РѠМЗРН  | PWM3DL  | PWM3DH | EF        |

| EO        | ACC    | SPSTA   | SPCON   | SPDAT  |        |         |         |        | E7        |

| D8        |        |         | I2CDAT  | I2CADR | I2CCON | I2CSTA  |         |        | DF        |

| DO        | PSW    |         | TKWKL0  | TKWKH0 | TKWKL1 | TKWKH1  | DADAT0  | DADAT1 | D7        |

| <b>C8</b> | T2CON  | T2MOD   | CRCL    | CRCH   | TL2    | TH2     |         |        | CF        |

| C0        | IRCON  | IP1H    |         |        |        |         |         |        | C7        |

| <b>B8</b> | IE1    | IP1     |         |        | KBCON  | CMPCON0 | CMPCON1 |        | BF        |

| <b>B0</b> |        | IP0H    | P0M1    | P0M0   | P1M0   | P1M1    | P2M0    | P2M1   | <b>B7</b> |

| A8        | IE0    | IP0     |         |        | ASW0   | ASW1    | PSFT0   | PSFT1  | AF        |

| AO        | P2     | TKDATL  | TKDATH  | TKCHS0 | TKCHS1 | TKCON0  | TKCON1  | TKCON2 | A7        |

| 98        | SCON   | SBUF    |         |        |        | TKADCF  | TKCSCF  | TKCSOF | 9F        |

| 90        | P1     |         |         |        |        |         | SCKCON  | EECON  | 97        |

| 88        | TCON   | TMOD    | TL0     | TL1    | TH0    | TH1     | CKCON   | TCKCON | 8F        |

| 80        | P0     | SP      | DPL     | DPH    |        |         | WDTCON  | PCON   | 87        |

Table 7-1 Special Function Registers Locations

The 16 addresses from SFR space are both byte- and bit-addressable. The bit-addressable SFRs are registers which addresses end with 000'b (80'h, 88'h, 90'h ... F8'h). Those 16 registers (128 bits) together with 128 bits from internal data memory (locations 20'h ... 2F'h) form the bit-addressable space.

| Hex/                                                                                            | X000                                                                                                                       | X001           | X010           | X011                      | X100                    | X101           | X110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | X111                                                                                                                                         | Bin/                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------|---------------------------|-------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bin                                                                                             |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | Hex                                                                                                                                                                                                            |

|                                                                                                 |                                                                                                                            |                |                | SF                        | 'R                      | 1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | 1                                                                                                                                                                                                              |

| F8                                                                                              |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | FF                                                                                                                                                                                                             |

| FO                                                                                              |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | F7                                                                                                                                                                                                             |

| E8                                                                                              |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | EF                                                                                                                                                                                                             |

| EO                                                                                              |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | E7                                                                                                                                                                                                             |

| D8                                                                                              |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | DF                                                                                                                                                                                                             |

| <b>D</b> 0                                                                                      |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | D7                                                                                                                                                                                                             |

| <b>C8</b>                                                                                       |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | CF                                                                                                                                                                                                             |

| C0                                                                                              |                                                                                                                            |                |                |                           |                         |                | The second secon |                                                                                                                                              | C7                                                                                                                                                                                                             |

| <b>B8</b>                                                                                       |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | BF                                                                                                                                                                                                             |

| <b>B0</b>                                                                                       |                                                                                                                            |                |                |                           |                         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                              | <b>B7</b>                                                                                                                                                                                                      |