### **PL3392A**

# Secondary Feedback PWM Power Switch

### **Product Description**

PL3392A is a high performance and low cost current mode PWM controller which provides several special enhancements designed to meet low standby power requirements. The start-up current is very low, typically 5uA, and the operation current is also low. The "No Audio Noise Green Mode" function is integrated to improve the efficiency at light or no load conditions. This green-mode function enables the power supply to meet even the strictest power conservation requirements easily.

The built-in slope compensation ensures the stability of peak current mode control. The integrated frequency jitter function helps to reduce EMI emission of a power supply with minimum line filters.

PL3392A also offers rich protection features including Cycle-by-Cycle peak current limiting, UVLO, VDD over voltage, load OVP, OLP, and OTP.

### **Pin Configuration**

### **Key Features**

- Very Low Start-up Current and Operating Current

- No Audio Noise Green Mode PWM Control

- Frequency Jitter Function to Improve EMI Performance

- Built-in Slope Compensation

- Leading Edge Blanking on CS Pin

- Cycle-by-Cycle peak current limiting

- VDD OVP and Under-voltage Lockout

- OLP (Over Load Protection)

- OUT OVP

- OTP

- Built-in Soft Start

- Drive voltage clamp

### **Applications**

AC/DC power supply applications

- Power Adaptor

- · Battery Charger

- PC 5V Standby Power

- Set Top Box Power Supply

Datasheet PL3392A

### 1 Overview

PL3392A is a high performance and low cost current mode PWM controller which provides several special enhancements designed to meet low standby power requirements. The start-up current is very low, typically 5uA, and the operation current is also low. The "No Audio Noise Green Mode" function is integrated to improve the efficiency at light or no load conditions. This green-mode function enables the power supply to meet even the strictest power conservation requirements easily.

The built-in slope compensation ensures the stability of peak current mode control. The integrated frequency jitter function helps to reduce EMI emission of a power supply with minimum line filters.

PL3392A also offers rich protection features including Cycle-by-Cycle peak current limiting, UVLO, VDD over voltage, load OVP, OLP, and OTP.

PL3392A is offered in DIP7 package.

### 2 Features

- Very Low Start-up Current and Operating Current

- No Audio Noise Green Mode PWM Control

- Frequency Jitter Function to Improve EMI Performance

- Built-in Slope Compensation

- Leading Edge Blanking on CS Pin

- Cycle-by-Cycle peak current limiting

- VDD OVP and Under-voltage Lockout

- OLP (Over Load Protection)

- OUT OVP

- OTP

- Built-in Soft Start

- Drive voltage clamp

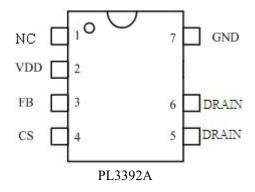

## 3 Pin Diagrams

### 4 Pin Description

| Pin   | Description                                                                |

|-------|----------------------------------------------------------------------------|

| VDD   | IC power supply.                                                           |

| NC    | Floating pin                                                               |

| FB    | Feedback input pin receive the feedback signal from the second side via an |

|       | opto-coupler and control the CS peak value and operating frequency.        |

| CS    | Current sense pin. Connected to an external voltage sense resistor.        |

| DRAIN | MOS drain                                                                  |

| GND   | IC ground.                                                                 |

### 5 Absolute Maximum Ratings

Absolute maximum ratings are the parameter values or ranges which can cause permanent damage and affect device reliability if exceeded.

| Parameter                    | Symbol | Value       | Units |

|------------------------------|--------|-------------|-------|

| DC Supply Voltage Range      | VDD    | -0.3 to +30 | V     |

| CS Input                     | CS     | -0.3 to +5  | V     |

| FB Input                     | FB     | -0.3 to +5  | V     |

| Maximum Junction Temperature | Tjmax  | 150         | °C    |

| Storage Temperature          | Tsto   | -55 to 150  | °C    |

**Note:** These are stress ratings only. Stress beyond these limits may cause permanent damage to the device. Functional operation of the device at these or any conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rated conditions for extended periods of time may affect device reliability.

# **6 Recommended Operating Conditions**

| Parameter                     | Min | Max  | Unit         |

|-------------------------------|-----|------|--------------|

| Operating Ambient Temperature | -40 | +105 | $^{\circ}$ C |

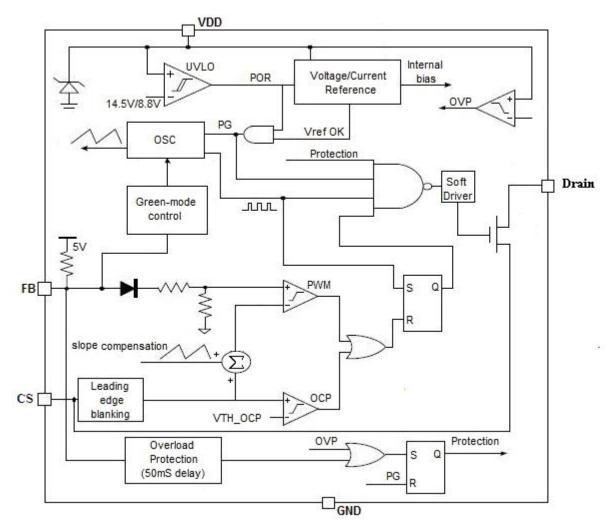

## 7 Block Diagram

PL3392A

Datasheet PL3392A

# **8 Electrical Characteristics**

(VDD =16V,  $T_A$  = 25 C, unless otherwise specified)

| Parameter                                    | Symbol                 | Test Conditions     | Min | Тур | Max | Unit         |

|----------------------------------------------|------------------------|---------------------|-----|-----|-----|--------------|

| VDD SECTION (VDD)                            |                        |                     |     |     |     |              |

| VDD Start up Current                         | IDD_st                 | VDD=VDD_ON-0.5V     |     | 5   | 20  | uA           |

| VDD UVLO Exit                                | VDD_ON                 | VDD rise            |     | 18  |     | V            |

| VDD UVLO Enter                               | VDD_OFF                | VDD fall            |     | 8   |     | V            |

| VDD Over Voltage Protection Level            | VDD_OVP                | VDD rise            |     | 28  |     |              |

| Operating Supply Current                     | IDD_op                 | V <sub>FB</sub> =3V |     | 1.2 |     | mA           |

| FEEDBACK SECTION (FB)                        |                        |                     |     |     |     |              |

| FB Open Loop Voltage                         | V <sub>FB</sub> _open  |                     |     | 5   |     | V            |

| FB Pin Short Circuit Current                 | I <sub>FB</sub> _short |                     |     | 0.3 |     | mA           |

| Burst Mode FB Vth                            | V <sub>TH</sub> _0D    |                     |     | 1.4 |     | V            |

| Over Load Protection FB Threshold Voltage    | V <sub>TH</sub> _PL    |                     |     | 4.3 |     | V            |

| OLP Delay Time                               |                        |                     |     | 50  |     | ms           |

| CURRENT SENSE SECTION                        | CS)                    |                     | -   |     | •   |              |

| Soft start time                              | T_soft                 |                     |     | 4   |     | ms           |

| Leading Edge Blanking Time                   | T_LEB                  |                     |     | 300 |     | ns           |

| Propagation Delay Time                       | Td_ocp                 |                     |     | 120 |     | ns           |

| Over Current Protection Threshold Voltage    | Vth_OCP                |                     | 720 | 750 | 780 | mV           |

| OSCILLATOR (FOSC)                            |                        |                     |     | •   | •   | '            |

| Normal PWM Frequency                         | Fop                    |                     | 50  | 55  | 60  | KHz          |

| Maximum Duty Cycle                           | Dmax                   | VFB=3V, CS=0        |     | 75  |     | %            |

| Green-mode Minimum Frequency                 | F_Burst                |                     |     | 22  |     | KHz          |

| Frequency Jitter Range                       |                        |                     | -4  |     | +4  | %            |

| ОТР                                          |                        |                     |     |     |     |              |

| Over temperature protection                  | TREG                   |                     |     | 145 |     | $\mathbb{C}$ |

| point                                        | INLO                   |                     |     | 143 |     |              |

|                                              |                        |                     |     |     |     |              |

| PL3392A(DIP7)                                |                        |                     |     |     |     |              |

| MOSFET <b>drain-source</b> breakdown voltage | BVdss                  |                     | 650 |     |     | V            |

| Static drain to source on resistance         | Rdson                  | Vgs=10V, Id=0.6A    |     | 4.4 |     | Ω            |

|                                              | 1                      |                     |     | 1   | 1   | 1            |

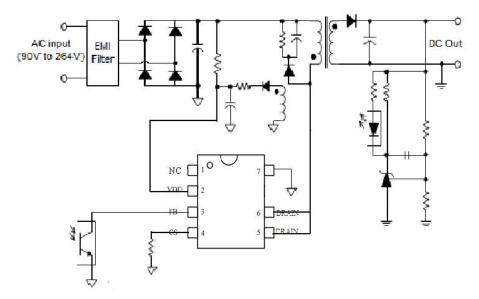

# 9 Application

### **Application Notes**

PL3392A includes all necessary function to build an easy and cost effective solution for low power supplies to meet the international power conservation requirements.

### 9.1 Startup & Operating Current

PL3392A has a very low start-up current typically 5uA, and the operation current is also low, typically 1.2mA. In "No Audio Noise Green Mode", the operation current is typically 0.6mA, so we could get high efficiency especially in light load.

#### 9.1 Soft Start

PL3392A features an internal 4ms (typical) soft start to soften the electrical stress occurring in the power supply during startup. It is activated during the power on sequence. As soon as VDD reaches VDD\_ON, the peak current is gradually increased from nearly zero to maximum 0.75V. Every restart up is followed by a soft start.

# 9.3 No Audio Noise Green-mode Operation

At light load or no load condition, the switching loss become the major loss of the power supply. To power dissipation in light and no load conditions, PL3392A adaptively adjust the

switching mode according to the load condition based on the voltage of FB pin. In light load condition, the FB voltage will decrease, when VFB is lower than a set threshold voltage, the power supply enters into green-mode operation and the PWM frequency will continuously be decreased, the minimum frequency is set about 20kHZ. When VFB voltage decreases further, the power supply will enter into burst mode operation to decrease the power dissipation at no load condition. Besides, there is no audible noise in any load condition.

### 9.4 Frequency Jitter

The frequency jitter function is integrated in the controller, the jitter is modulated by a periodic signal, the modulate signal frequency is much smaller than the oscillator frequency, by this way, the EMI noise has a wider spectrum with lower amplitudes.

# 9.5 Current Sensing and Leading Edge Blanking

The typical current mode of PWM controller feedbacks both current signal and voltage signal to close the control loop and achieve regulation. The PL3392A detects the primary MOSFET current from the CS pin, which is not only for the peak current mode control but also

Datasheet PL3392A

for the cycle-by- cycle current limit. Each time when the power MOSFET is switched on, a turn-on spike will inevitably occur on the sense-resistor. To avoid premature termination of the switching pulse, a 300nS leading-edge blanking time is built in. Conventional RC filtering can therefore be omitted. During this blanking period, the current-limit comparator is disabled and it cannot switch off the gate driver.

### 9.6 Built-in Slope Compensation

The sensed voltage across the CS resistor is used for PWM control, and cycle by cycle

current limit, Built-in slope compensation circuit adds a voltage ramp onto the current sense input voltage. This greatly improves the close loop stability and prevents the sub-harmonic oscillation of peak current mode PWM control scheme.

#### 9.7 Protection Control

PL3392A has built-in rich protection features including Cycle-by-Cycle Current Limiting, VDD over voltage, Under Voltage Lockout on VDD, Output OVP, OLP and OTP Protection.

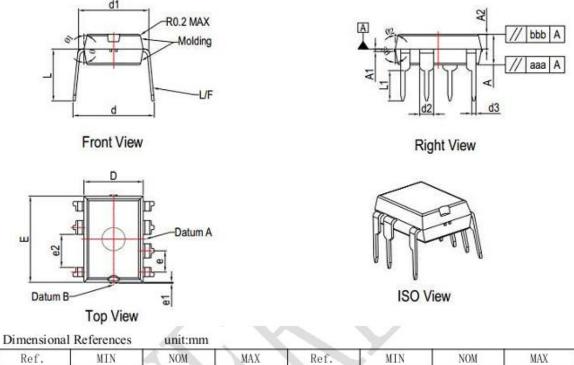

# 10 Packaging Information

### DIP7 Packaging

| Ref. | MIN        | NOM        | MAX    | Ref. | MIN        | NOM | MAX |  |

|------|------------|------------|--------|------|------------|-----|-----|--|

| A    | 3. 224     | 3. 274     | 3. 324 | e    | 2. 54 BSC  |     |     |  |

| A1   | -          | 0. 254 BSC |        | e1   | 1          | 1   | 0.1 |  |

| A2   | 1, 54      | 1.59       | 1.64   | e2   | 3. 556 BSC |     |     |  |

| D    | 6. 33      | 6. 38      | 6.43   | L    | 5. 57 REF  |     |     |  |

| d    | 8. 42      | 8. 72      | 9.02   | L1   | 3. 0       | 3.3 | 3.6 |  |

| d1   | 7. 32      | 7. 62      | 7.92   | Φ    | 9"         | 10° | 11" |  |

| d2   | 1. 524 BSC |            |        | Ф1   | 11°        | 12° | 13° |  |

| d3   | 0. 457 BSC |            |        | Ф2   | 11"        | 12° | 13° |  |

| Е    | 9. 2       | 9, 25      | 9.3    | Ф3   | 9°         | 10° | 11" |  |

| aaa  | 0.10       |            |        | bbb  | 0.10       |     |     |  |

## 11 Important Notice

POWERLINK reserves the right to make changes or corrections to its products at any time without notice. Customers should verify the datasheets are current and complete before placing orders.